Опытные оверклокеры наверняка помнят, что при повышении частоты

тактового генератора опорной частоты на процессорах Athlon 64 было

необходимо понижать множитель шины HyperTransport, чтобы эффективная

тактовая частота не сильно уходила за порог в 1000 МГц. Превышение

этого порога пагубно сказывалось на стабильности и ограничивало разгон,

поэтому при повышении опорной частоты с 200 МГц до 300 МГц множитель

опускали с 5х до 3х, что давало результирующую частоту 900 МГц. В процессорах Intel Core i7 результирующая частота шины QPI формируется

аналогичным образом, посредством генератора опорной частоты и

множителя. Однако множитель шины QPI заблокирован для всех процессоров,

кроме серии Extreme Edition и составляет 18х для Core i7-920 и Core

i7-940. У процессоров Core i7-965 существует возможность выбора между

18х, 20х и 24х. Таким образом, минимальный множитель составляет 18х и

способен в ряде случаев ограничивать разгонный потенциал процесса

упором в порог стабильной работы шины QPI. Как сообщают журналисты сайта ExpReview,

в процессорах семейства Core i5 множитель шины QPI будет составлять

16х. С точки зрения оверклокера, это даже хорошо, так как позволит

достигать больших частот тактового генератора и, следовательно, ядер

процессора. В современных процессорах Core i7 порог стабильности

пролегает в районе 8 миллиардов транзакций в секунду, что соответствует

частоте тактового генератора 220 МГц при множителе 18х, а при множителе

16х для достижения этого порога потребуется частота 250 МГц. Впрочем,

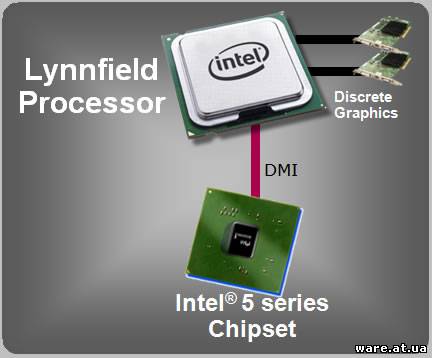

возникает закономерный вопрос – а зачем в процессорах Core i5 шина QPI,

если связь процессора с чипсетом будет осуществляться посредством шины

DMI?

Как нам уже известно, контроллер шины PCI Express будет

интегрирован в Core i5, перенеся, по сути, остатки функционала

северного моста под крышку процессора. Однако реализация контроллера

PCI Express весьма необычна. В отличие от остальных “кирпичиков”

архитектуры Nehalem, таких как контроллер памяти или процессорные ядра,

контроллер PCI Express не будет являться агентом внутренней кольцевой

шины. Коммутация с процессоров будет осуществляться посредством шины

QPI, чей множитель и составит в Core i5 всего 16х. Это позволит достичь

пропускной способности около 4.2 миллиарда транзакций, что

соответствует эффективной скорости передачи данных около 17 Гбайт в

секунду и перекрывает потребности контроллера PCI Express 2.0 х16,

которые составляют 16 Гбайт в секунду.

Источник: http://www.overclockers.ru/hardnews/32838.shtml |